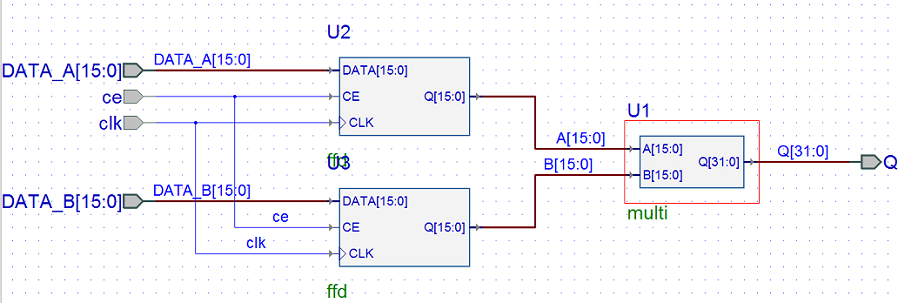

Figure 3 from Teaching and research in FPGA based Digital Signal Processing using Xilinx System Generator | Semantic Scholar

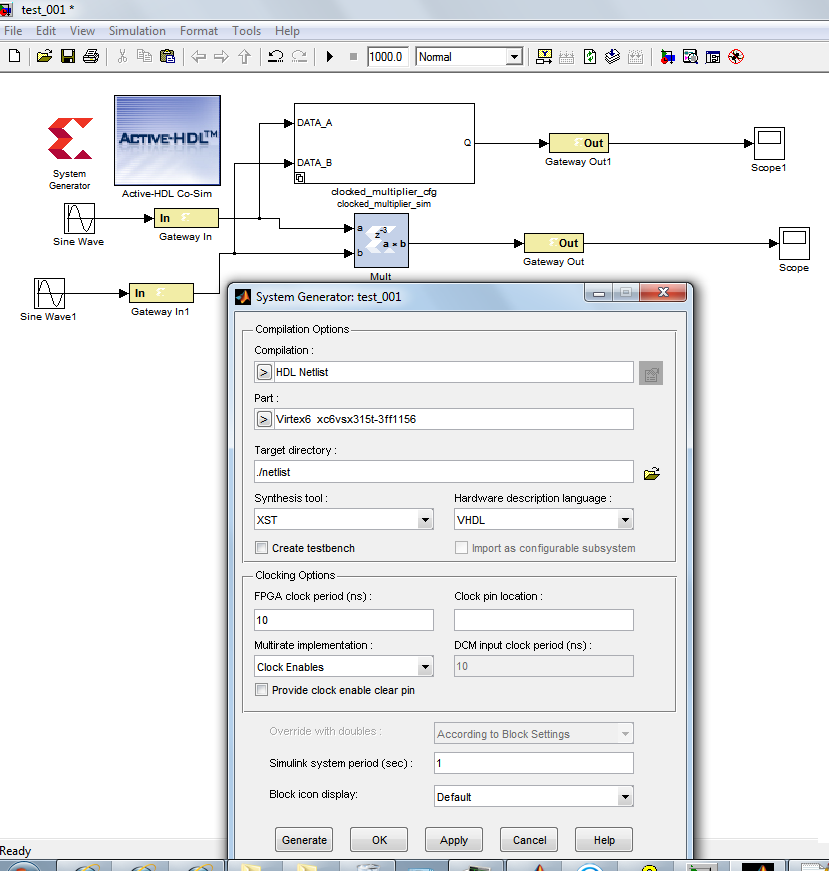

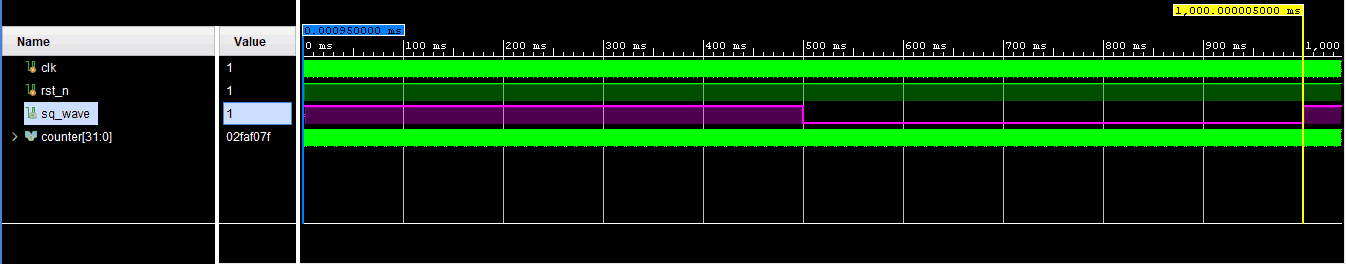

Xilinx System Generator with Active-HDL - Application Notes - Documentation - Resources - Support - Aldec

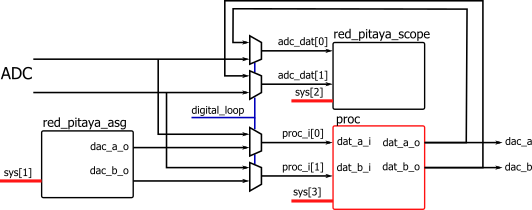

Spectral subtraction architecture based on Xilinx system generator... | Download High-Resolution Scientific Diagram

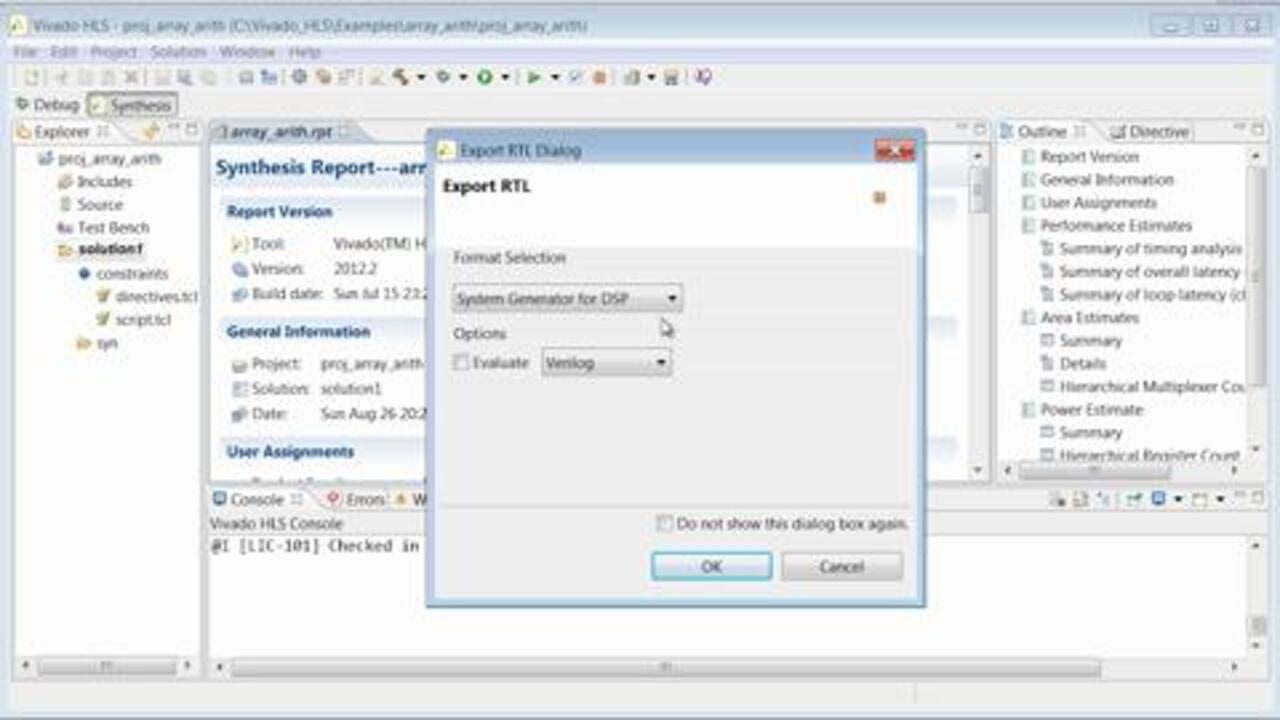

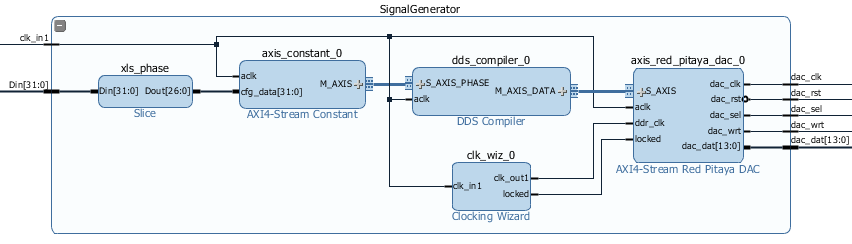

DDS Compiler(Direct Digital Synthesizer)/Analog Signal Generation of Zynq Processor in VIVADO. - YouTube